Intel Xeon Sapphire Rapids: How To Go Monolithic with Tiles

by Dr. Ian Cutress on August 31, 2021 10:00 AM ESTAdd In Some HBM, Optane

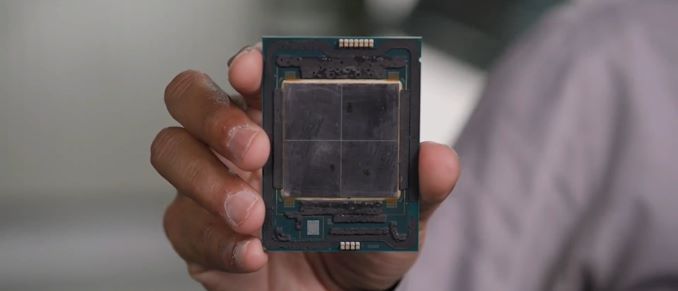

The other angle to Sapphire Rapids is the versions with HBM on board. Intel announced this back in June, but there haven’t been many details. As part of Architecture Day, Intel stated that that HBM versions of Sapphire Rapids would be made public, and be made socket compatible with standard Sapphire Rapids. The first customer of the HBM versions of SPR is the Argonne National Lab, as part of its Aurora Exascale supercomputer.

This diagram it showcases four HBM connections, one to each compute tile. Looking at the package, however, I don’t think that there’s realistically enough space unless Intel has commissioned some novel HBM that is long and narrow as it is in the diagram.

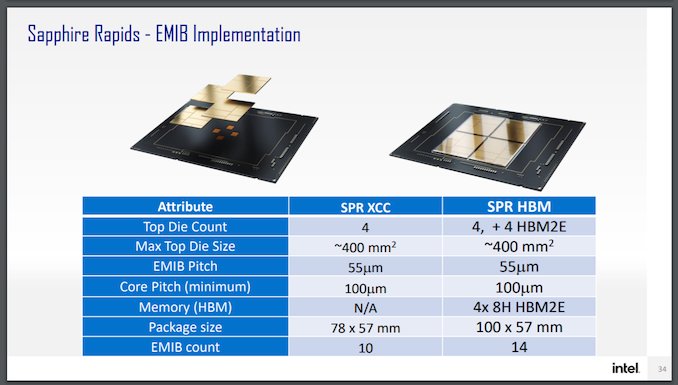

Even though Intel said that the HBM variants would be in the same socket, even their own slide from Hot Chips says different.

Here the package size with HBM says 100x57mm, compared to the SPR which is 78x57mm. So unless Intel is planning a reduced version for the 78x57mm socket, it's going to be in a different socket.

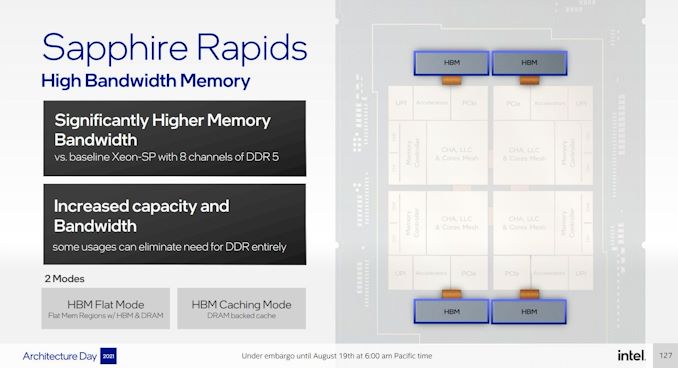

It is important to note that HBM will act in a similar capacity to Optane – either as an HBM flat mode with DRAM that equates the two, or as an HBM caching mode that acts similar to an L4 cache before hitting main memory. Optane on top of this can also be in a flat mode, a caching mode, or as a separate storage volume.

HBM will add power consumption to the package, which means we’re unlikely to see the best CPU frequencies paired with HBM if it is up against the socket limit. Intel has not announced how many HBM stacks or what capacities will be used in SPR, however it has said that they will be underneath the heatspreader. If Intel are going for a non-standard HBM size, then it’s anyone’s guess what the capacity is. But we do know that it will be connected to the tiles via EMIB.

A side note on Optane DC Persistent Memory – Sapphire Rapids will support a new 300 series Optane design. We asked Intel if this was the 200-series but using a DDR5 controller, and were told that no, this is actually a new design. More details to follow.

UPI Links

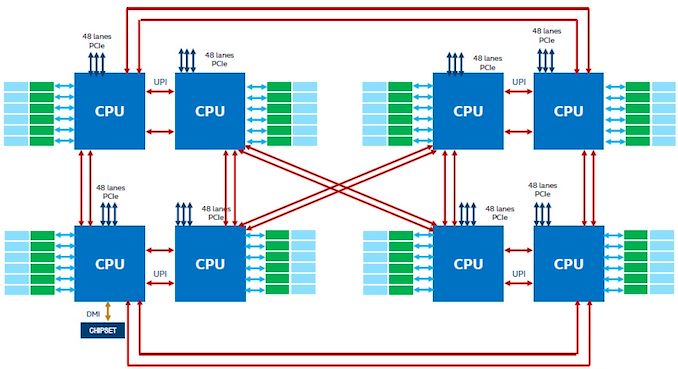

Each Sapphire Rapids Processor will have up to four x24 UPI 2.0 links to connect to other processors in a multi-socket design. With SPR, Intel is aiming for up to eight socket platforms, and in order to increase bandwidth has upgraded from three links in ICL to four (CLX had 2x3, technically), and moved to a UPI 2.0 design. Intel would not expand more on what this means, however they will have a new eight-socket UPI topology.

Current eight-socket designs use a twisted hypercube topology: two groups of four form a box, and one pair is connected to the same vertex on the other set of four, while the second pair is inverted. Make sense? No, not really. Essentially each CPU is directly connected to three others, and the other four are two hops away. With the new topology, each CPU gets a direct connection to another, which moves the design more towards a fully connected topology, however exactly which CPU that connection should go to, Intel hasn’t stated yet.

Security

Intel has stated that it will be announcing full Security updates for SPR at a later time, however features like MKTME and SGX are key priorities.

Conclusions

For me, the improved cores, upgraded PCIe/DDR, and the ‘appears as a monolith’ approach are the highlights to date. However, there are some very obvious questions still to be answered – core counts, power consumption, how lower core counts would work (even suggestions that the LCC version is actually monolithic), and what the HBM enabled versions will look like. The HBM versions, with the added EMIB, are going to cost a good amount, which isn’t great at a time when AMD’s pricing structure is very competitive.

It is expected that when Sapphire Rapids is released, AMD will still be in the market with Milan (or as some are postulating, 3D V-Cache versions of Milan, but nothing is confirmed) and it won’t be until the end of 2022 when AMD launches Zen 4. If Intel can execute and bring SPR into the market, it will have a small time advantage in which to woo potential customers. Ice Lake is being sold on its specific accelerator advantages, rather than raw core performance, and we will have to wait and see if Sapphire Rapids can bring more to the table.

Intel moving to a tile/chiplet strategy in the enterprise has been expected for a number of years – at least on this side of the fence, ever since AMD made it work and scale beyond standard silicon limits, regardless of whatever horse-based binding agent is used between the silicon, Intel would have to go down this route. It has been delayed, mostly due to manufacturing but also optimizing things like EMIB which also takes time. EMIB as a technology is really impressive, but the more chips and bridges you put together, even if you have a 99% success rate, that cuts into yield. But that's what Intel has been working on, and for the enterprise market, Sapphire Rapids is the first step.

94 Comments

View All Comments

dullard - Tuesday, August 31, 2021 - link

"Set to launch in 2022, Sapphire Rapids will be Intel’s first CPU product to take advantage of a multi-die architecture". Doesn't that comment forget the Pentium D, Kentsfield, etc?Ian Cutress - Tuesday, August 31, 2021 - link

You're meant to take the rest of that sentence as well :) I've updated it to make it clearer.dullard - Tuesday, August 31, 2021 - link

Thanks, the edit works quite well. It is just a pet peeve of mine. You could have also been more blunt and I would have been fine (Intel's first tiled approach was clumsy at best).TrevorH - Tuesday, August 31, 2021 - link

I Think you could have just put a full stop on the end of "Set to launch in 2022, Sapphire Rapids will be Intel’s first modern CPU product"Kevin G - Tuesday, August 31, 2021 - link

If you want to go waaaaaay back, there is the Pentium Pro with its separate L2 cache die on package.There is also Westmere which had a 32 nm CPU and 45 nm north bridge in the same package. There are also a slew of recent mobile multi-die packages that integrate the chipset on package to reduce board area.

ballsystemlord - Tuesday, August 31, 2021 - link

The Intel Pentium D was also multi-die. I know, I took one apart. I have pictures.jordanclock - Tuesday, August 31, 2021 - link

I'm not sure if I would call duct taping together two P4s as architecture as much as it was jerry rigged.GNUminex_l_cowsay - Tuesday, August 31, 2021 - link

All of the renders and block diagrams make it look like Intel made two mirrored dies of what is otherwise the same chip design. Did Intel say anything about that?Ian Cutress - Tuesday, August 31, 2021 - link

Yup, that's in the article.yannigr2 - Tuesday, August 31, 2021 - link

Just 4 CPUs glued together but with 2021 marketing in the presentation.