Memblaze Launches PBlaze5 SSDs: Enterprise 3D TLC, Up to 6 GB/s, 1M IOPS, 11 TB

by Anton Shilov on June 24, 2017 10:00 AM EST

Memblaze has introduced its new generation of server-class NVMe SSDs for mixed and mission critical workloads. The PBlaze5 SSDs are based around Micron's 3D eTLC memory and paired with a Microsemi Flashtec controller. The SSDs come in PCIe 3.0 x8 AIC or 2.5” U.2 form-factors, carry up to 11 TB of 3D TLC NAND, and feature sequential read performance of up to 6 GB/s as well as random read performance of up to 1M IOPS.

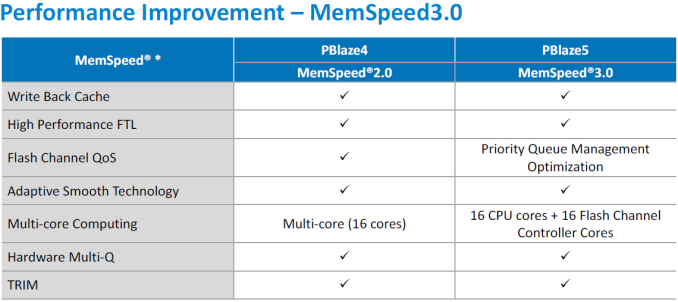

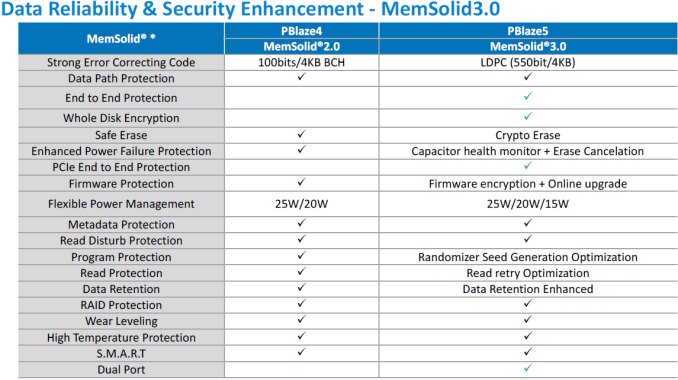

The Memblaze PBlaze5 700 and 900-series SSDs are based on Microsemi’s Flashtec PM8607 NVMe2016 controller that features 16 compute cores, 32 NAND flash channels, and supports everything one might expect from a contemporary SoC for server SSDs (LDPC 550 bit/4KB ECC with a <1 bit per 1017 bit error rate, NVMe 1.2a, AES-256 PCIe 3.0 x8/PCIe 3.0 x4 dual-port, etc.) along with a host of enterprise-grade features. Memblaze further outfits the card with their own MemSpeed 3.0 as well as MemSolid 3.0 firmware-based technologies. The MemSpeed 3.0 feature better ensures consistent performance and QoS, and comes with further priority que management optimizations over the previous version. As for the MemSolid 3.0, it is a stack of reliability and security features of the PBlaze5 900-series drives, which we are going to touch upon later.

Both the 700 and 900 series drives use the same kind of memory — Micron’s 32-layer 3D eTLC NAND flash (384 Gb). Memblaze tells us that the 3D eTLC memory offers higher endurance and reliability, but it does not go beyond that.

Given the same controller and the same kind of memory, performance and power consumption numbers for the PBlaze5 700 and 900-series SSDs are close (the 900-series offers 50% higher random write performance). The 2.5" drive form-factor PBlaze5 D700/D900 feature sequential read speeds of up to 3.2 GB/s, sequential write speeds of up to 2.4 GB/s, as well as up to 760K random read IOPS. The PCIe card-based PBlaze5 C700/C900 offer considerably higher performance numbers due to two times wider interface (PCIe 3.0 x8): sequential reads up to 6 GB/s, sequential writes up to 2.4 GB/s, and 1.042M read IOPS, respectively. As for power consumption, all the drives use from 7 to 25 W of power, depending on the configuration, workload and settings. However, the similarities between the PBlaze5 700 and 900-series SSDs end here.

The PBlaze5 700 drives are designed for datacenters that require maximum performance, high density and capacity at low power and moderate costs. That said, the PBlaze 700-series are rated for 1 DPWD for five years and come with reliability features that are consistent with other SSDs for hyperscale datacenters.

By contrast, the PBlaze5 900-series drives are aimed at mission critical environments (databases, financial transactions, analytics, etc.) that need enhanced reliability. In addition to extended error correction code (with a 1x10-17 bit error rate), the PBlaze 900-series also supports end-to-end data path protection compatible with T10 Data Integrity Field (DIF)/SNIX DIX, which results in a Silent Bit Error Rate (SBER) lower than 1 bit per 1023 bits read. In addition, the 900-series takes full advantage of all MemSolid 3.0 enhancements offering features like crypto erase, background scan protection, firmware encryption (one of the first SSDs to support this feature), whole disk encryption, metadata protection, read disturb protection, dual-port capability (U.2 drives only), and so on. For those who need to flexibly manage the power consumption of their SSDs, the MemSolid 3.0-based drives offer distinct 15, 20 and 25 W modes. As for endurance, Memblaze guarantees 3 DPWD over five years for its PBlaze5 900-series SSDs.

| Memblaze PBlaze5 Series Specifications | |||||

| PBlaze5 D700 | PBlaze5 C700 | PBlaze5 D900 | PBlaze5 C900 | ||

| Form Factors | 2.5" U.2 Drive | HHHL AIC | 2.5" U.2 Drive | HHHL AIC | |

| Interface | PCIe 3.0 x4 | PCIe 3.0 x8 | PCIe 3.0 x4 | PCIe 3.0 x8 | |

| Capacities | 2 TB 3.6 TB 4 TB 8 TB 11 TB |

2 TB 3.2 TB 4 TB 8 TB |

|||

| Controller | Microsemi Flashtec PM8607 NVMe2016 | ||||

| Protocol | NVMe 1.2a | ||||

| NAND | 3D Enterprise TLC NAND memory | ||||

| Sequential Read | 3.2 GB/s | 6 GB/s | 3.2 GB/s | 6 GB/s | |

| Sequential Write | 2.4 GB/s | 2.4 GB/s | 2.4 GB/s | 2.4 GB/s | |

| Random Read (4 KB) IOPS | 760,000 | 1,042,000 | 760,000 | 1,042,000 | |

| Random Write (4 KB) IOPS | 210,000 | 304,000 | |||

| Latency Read | 90 µs | ||||

| Latency Write | 15 µs | ||||

| Power | Idle | 7 W | |||

| Operating | 25 W | ||||

| ECC | LDPC 550 bit/4 KB | ||||

| Endurance | 1 DWPD | 3 DWPD | |||

| Dual-Port Support | - | + | - | ||

| Uncorrectable Bit Error Rate | <1 bit per 1017 bits read | ||||

| Silent Bit Error | - | <1 bit per 1023 bits read | |||

| End-to-End Data Protection | - | T10 DIF/DIX | |||

| Crypto Erase | - | + | |||

| Firmware Signature | - | + | |||

| PCIe ECRC | - | + | |||

| Encryption | AES-256 | ||||

| Power Loss Protection | Yes | ||||

| Proprietary Technologies | MemSpeed 3.0 MemSolid 3.0 |

MemSpeed 3.0 MemSolid 3.0 |

|||

| MTBF | 2.1 million hours | ||||

| Warranty | Five years | ||||

| Additional Information | Link | Link | |||

Traditionally, Memblaze does not publicly list the pricing of their enterprise SSDs, as pricing is dependent in part on the number ordered and just how the customer wants the drives configured. The company is currently working with its partners on deploying the PBlaze5 drives, and actual volume shipments will begin after their clients validate the SSDs with their respective applications.

Related Reading:

- Intel Announces SSD DC P4501 Low-Power NVMe SSD With 3D NAND

- Western Digital Launches HGST Ultrastar SS300 SSDs: 3D NAND for Data Centers

- Intel Announces New DC P4500 And P4600 Datacenter SSDs

- The Intel Optane SSD DC P4800X (375GB) Review: Testing 3D XPoint Performance

- Samsung Shows Off A Z-SSD: With New Z-NAND

- NGD Launches Catalina: a 24 TB PCIe 3.0 x4 SSD with 3D TLC NAN

Source: Memblaze

19 Comments

View All Comments

R0H1T - Saturday, June 24, 2017 - link

I definitely want one, or two. Memblaze can probably send a few for (home) server reviews ^_^Bullwinkle J Moose - Saturday, June 24, 2017 - link

Can we haz PCIe 4.0 X 16 next year and PCIe 5 in 2019 ?cnom now....FIGHT FIGHT FIGHT FIGHT!

damianrobertjones - Monday, June 26, 2017 - link

No you cannot! You will have a small, minor, speed increase but ONLY once sales start to fall on the current boards. Please understand that we must max the $$$$.asmian - Saturday, June 24, 2017 - link

>a 1x10^17 bit error rate> a Silent Bit Error Rate (SBER) lower than 10^23

1x10^17 is just 10^17 - this info is utterly meaningless. As is the 10^23 number. I presume you meant to say 1 in 10^17, and 1 in 10^23.

Either sloppy cut'n'paste from the marketing, or poor understanding of what the bit error rate numbers represent, either of which isn't good for a tech site author. :(

XZerg - Saturday, June 24, 2017 - link

now 10^-17 or 10^-23remove the "-", it should just be 10^17 or 10^23

rems - Saturday, June 24, 2017 - link

Think so too!Tadashi130 - Saturday, June 24, 2017 - link

Actually the article said 1×10^-17. See the minus sign? Which implies 1/(10^17) Which implies 1 in 10^17. The article is right.But the table should not have the minus sign for the power as it says "1 bit per ...".

It doesn't look at all to me a poor understanding. The table error is obviously an oversight. Excuse them for being mere humans that sometimes make small mistakes.

asmian - Sunday, June 25, 2017 - link

Nah, the edit has made things worse. The principle of a bit error rate is that it is quoted as less than one error in (hopefully) a *very* large number. Putting minus signs in the exponent makes the number a miniscule fraction instead. It's just factually wrong, and the article text hasn't been corrected for the original mistake in quoting the number alone (without the "one error in" info).Clearly the author doesn't understand at all what he's regurgitating.

ddriver - Monday, June 26, 2017 - link

1 out of 10 is the same as 0.1The minus says that the chance of a bit getting corrupt is 0.00000000000000001%

If there is one corrupt bit every 10^17 bits, then the odds of any one bit getting corrupt is 1 / 10^17 or interchangeably - 10^-17

So either leave it "1 per 10^17" or just "10^-17"

Because right now as it is - "1 bit per 10^-17 bits read" - means that each and every bit read will have 10^17 errors in it LOL. That's immensely worse than having 100% error rate LOL. If you have 1 error bit per each 10 attobits read, you will mount 100 peta errors until you are done reading a single whole bit.

ddriver - Monday, June 26, 2017 - link

Ops, that should be 0.000000000000001%