AMD “Rome” EPYC CPUs to Be Fabbed By TSMC

by Ryan Smith on July 26, 2018 11:00 AM EST

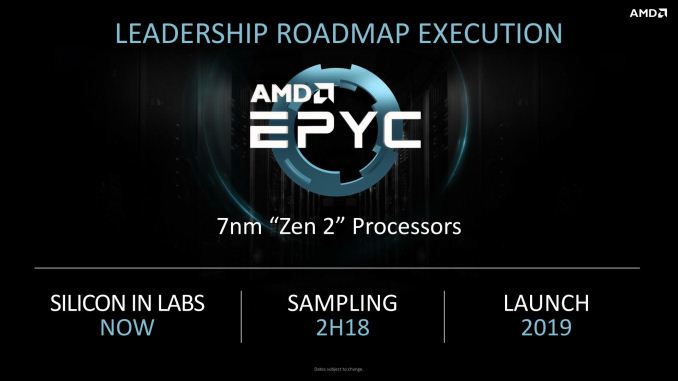

Along with AMD’s epic quarterly results that were announced yesterday afternoon, there was also an interesting nugget buried in the earnings call for the results. We’ve known for some time now that AMD was going to be working with both TSMC and fraternal fab GlobalFoundries to produce 7nm products, similar to what they’ve done for their current-generation 16nm/14nm products. However until now it hasn’t been clear how those products would be allocated – whether TSMC will once again just produce semi-custom APUs, or if they’ll do more. But now we have an answer thanks to AMD’s earnings call, and the answer is indeed “more”.

Specifically, AMD CEO Lisa Su has announced that second-generation “Rome” EPYC CPU that the company is wrapping up work on is being produced out at TSMC. This is a notable departure from how things have gone for AMD with the Zen 1 generation, as GlobalFoundries has produced all of AMD’s Zen CPUs, both for consumer Ryzen and professional EPYC parts.

So, Matt, on your first question relative to the manufacturing of the second generation of EPYC, so as I said earlier, we are working with both the TSMC and GLOBALFOUNDRIES in 7-nanometer. As for the 7-nanometer Rome that we're currently sampling, that's being manufactured at TSMC.

As it stands, AMD seems rather optimistic about how things are currently going. Rome silicon is already back in the labs, and indeed AMD is already sampling the parts to certain partners for early validation. Which means AMD remains on track to launch their second-generation EPYC processors in 2019.

Unfortunately, the call offered no real insight as to why AMD has shifted to using TSMC for some of their CPUs for this upcoming generation. AMD’s hands are somewhat tied on fab choice in as much as they have quotas under their wafer share agreement with GlobalFoundries that they must fulfill. How AMD wants to split that up is up to them, but beyond that AMD hasn’t offered any information as to why they’ve made the choices they have.

Ultimately however if they are meeting their order quota from GlobalFoundries, then AMD’s situation is ultimately much more market driven: which fab can offer the necessary capacity and performance, and at the best prices. Which will be an important consideration as GlobalFoundries has indicated that it may not be able to keep up with 7nm demand, especially with the long manufacturing process their first-generation DUV-based 7nm “7LP” process requires.

Source: AMD Q2'18 Earnings Call

32 Comments

View All Comments

JoeyJoJo123 - Thursday, July 26, 2018 - link

Zen2 EPYC sounds great. Can't wait for Zen2 arch to come to Threadripper platforms as well.jklw10 - Thursday, July 26, 2018 - link

32 core epyc with 4.5 ghz? yes please :DSaturnusDK - Thursday, July 26, 2018 - link

While you're overly optimistic about the frequency of a server CPU as 4.5GHz would be well outside the performance per Watt optimum even for a 7nm CPU, you are grossly underestimating the core count. EPYC2 or Rome will have at least 48c/96t and most rumours suggests 64c/128t on a single package for the top SKUs.Death666Angel - Friday, July 27, 2018 - link

Single or quad core turbo maybe? :)Santoval - Monday, July 30, 2018 - link

The best they could do is 3.8 - 3.9 GHz base, ~4.5 GHz turbo for all clocks (for 32 cores, make that 4.2 - 4.3 GHz turbo for 48 cores and, if they do release 64-core packages, 4 - 4.1 GHz turbo for all clocks, with a corresponding drop in base clocks for all) and perhaps up to a 4.8 - 4.9 GHz turbo for 1 & 2 cores.And that assumes that they would spend most of the 7nm node's additional power efficiency to higher clocks rather than other areas (i.e. in reworking the architecture), which is not at all certain. Frankly the above clocks would make more sense for a move of the Zen/Zen+ to 7nm, rather than Zen 2, which will sport a new architecture. How new it remains to be seen.

K_Space - Thursday, July 26, 2018 - link

Has TSMC historically produced "better" chips at given size relative to GloFo? or are these results of fallacies in the AT comment section I took to be fact?Arnulf - Thursday, July 26, 2018 - link

TSMC is actually producing huge monolithic chips (such as NVidia GPUs) for years now.Zeppelin dies manufactured by GF (employed in 1st generation Epyc CPUs) are what, one third the of the area of largest GPU/AI chips?

Spoelie - Friday, July 27, 2018 - link

Transistor performance is *arguably* more important for CPUsTransistor density is *arguably* more important for GPUs

So it might be that TSMC is better at building GPUs and GF better at building CPUs

I haven't seen any evidence for it either way - just not aware of any CPU designs clocking 4GHZ+ out of TSMC, but that doesn't necessarily mean they can't. Rome would be good counter evidence.

wumpus - Friday, July 27, 2018 - link

EPYC used the same die as Ryzen for a bunch of reasons:AMD claimed that it was cheaper to fab 4 ~200mm**2 chips than 1 ~700mm*2 chip. This might be GloFo specific and TSMC won't have a problem with a bigger chips (and obviously each core will be smaller in 7nm).

AMD didn't want to spend the money on multiple masks (although obviously they made another for their ALUs)

AMD's data bus/ring sucked so much that multiple CPUs wired together didn't lose performance. If they are on one big chip (which is sounds like), presumably they've fixed their data fabric.

Santoval - Monday, July 30, 2018 - link

Even if TSMC didn't have a problem with making huge monolithic dies AMD would have, since TSMC would charge them much more for each huge monolithic die than each 4 smaller dies, which would eat at AMD's margins. And that's because yields of huge dies are quite lower and they are more difficult to manufacture.Putting aside the non-issue of a monolithic Epyc or top-core TR die, each Zeppelin die will be smaller at 7nm only if the cores are the same or up to 12 (for 6 cores per CCX). If AMD moves to 16-core Zeppelin dies (with either two 8-core CCX blocks or, quite unlikely, four 4-core ones), either for Epyc only or also for TR and Ryzen, the dies will be either the same size (assuming exactly twice the density of both the FEOL and BEOL stack) or a bit larger (assuming a bit lower than double density).

So, if AMD can afford to move to 16-core dies, die-size and yield wise, they will. If not they will max out at 12-core dies and a 48-core Epyc. The question is, if they can only afford 16-core dies for Epyc, if they are going to fab both 12-core and 16-core dies, which would add to design costs but would save precious die space (from less disabling of cores). Designing both a 6-core CCX and an 8-core one would further inreace design costs.