PCI Express 7.0 Spec Hits Draft 0.3, 512GBps Connectivity on Track For 2025 Release

by Ryan Smith on June 13, 2023 2:30 PM EST

In what’s quickly becoming a very busy week for data center and high-performance computing news, the PCI Special Interest Group (PCI-SIG) is hosting its annual developers conference over in Santa Clara. The annual gathering for the developers and ecosystem members of the industry’s preeminent expansion bus offers plenty of technical sessions for hardware devs, but for outsiders the most important piece of news to come from the show tends to be the SIG’s annual update on the state of the ecosystem. And this year is no exception, with a fresh update on the development status of PCIe 7.0, as well as PCIe 6.0 adoption and cabling efforts.

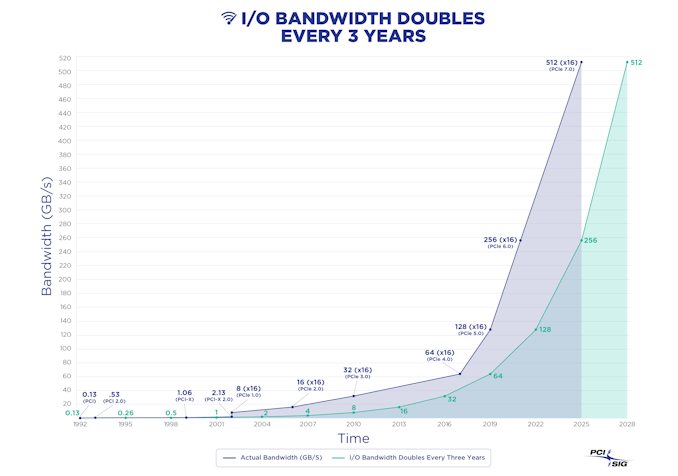

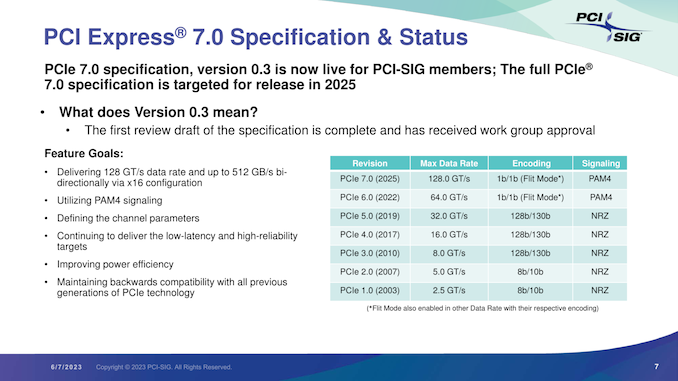

With PCI Express 6.0 finalized early last year, the PCI-SIG quickly moved on to starting development work on the next generation of PCIe, 7.0, which was announced at last year’s developer’s conference. Aiming at a 2025 release, PCIe 7.0 aims to once again double the amount of bandwidth available to PCIe devices, bringing a single lane up to 16GB/second of full-duplex, bidirectional bandwidth – and the popular x16 slot up to 256GB/second in each direction.

| PCI Express Bandwidth (Full Duplex: GB/second/direction) |

||||||||

| Slot Width | PCIe 2.0 (2007) |

PCIe 3.0 (2010) |

PCIe 4.0 (2017) |

PCIe 5.0 (2019) |

PCIe 6.0 (2022) |

PCIe 7.0 (Est. 2025) |

||

| x1 | 0.5GB/sec | ~1GB/sec | ~2GB/sec | ~4GB/sec | 8GB/sec | 16GB/sec | ||

| x2 | 1GB/sec | ~2GB/sec | ~4GB/sec | ~8GB/sec | 16GB/sec | 32GB/sec | ||

| x4 | 2GB/sec | ~4GB/sec | ~8GB/sec | ~16GB/sec | 32GB/sec | 64GB/sec | ||

| x8 | 4GB/sec | ~8GB/sec | ~16GB/sec | ~32GB/sec | 64GB/sec | 128GB/sec | ||

| x16 | 8GB/sec | ~16GB/sec | ~32GB/sec | ~64GB/sec | 128GB/sec | 256GB/sec | ||

At the time of last year’s announcement, early work was just beginning on PCIe 7.0. For their 2023 conference, the PCI-SIG has completed the first draft release of the specification, version 0.3, and is ready for distribution to the group’s members, marking the next step in the development of the standard.

Early drafts of PCI-SIG standards tend to be light on public technical details, and PCIe 7.0 v0.3 is no different in that regard. As a result, there is little new we know about the specification itself that wasn’t already outlined with the goals announced last year.

Still, the completion of the first draft of the specification is important, as it indicates that the group has been successful in developing the core technological underpinnings needed for ever-faster PCIe communications. That’s something that is no easy feat, given that PCIe 7.0 requires doubling the bus frequency at the physical layer, a major development that PCIe 6.0 sidestepped with PAM4 signaling. Even then, nothing comes for free in regards to improving data signaling, but with PCIe 7.0, the PCI-SIG is arguably back to hard-mode development by needing to improve the physical layer once more – this time to enable it to run at around 30GHz.

Electrically, PCIe 7.0 sticks with PAM4 + FLIT encoding, just like its predecessor. So what the next standard spends in physical layer development, it will largely be saving in development of its logical layer.

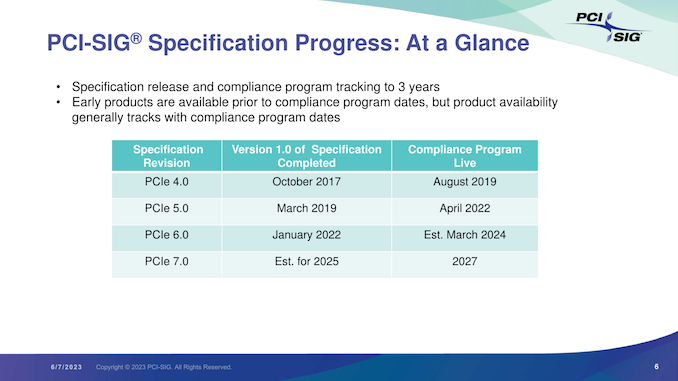

Ultimately, the PCI-SIG’s standards cadence is based around a three-year development cycle. As a result, this year’s draft announcement is right on schedule for the group, which expects it has another two years of development to go. Assuming the remaining draft work goes well, the PCI-SIG is expecting to have the PCIe 7.0 specification finalized in 2025.

A compliance program for the specification, in turn, should be up and running in 2027. The compliance programs are the functional barometer for hardware availability, as compliance testing and certification is effectively necessary before any large-scale commercial hardware using the new spec can ship. And with few exceptions, these tend to take 2 to 2.5 years to put together. All of which is to say that the first commercial PCIe 7.0 products are not expected until at least 2027 – five years from now – underscoring that there is still a lot of work to go for PCIe 7.0 following this initial draft.

PCIe 5.0/6.0 Cabling Coming Along For Late 2023

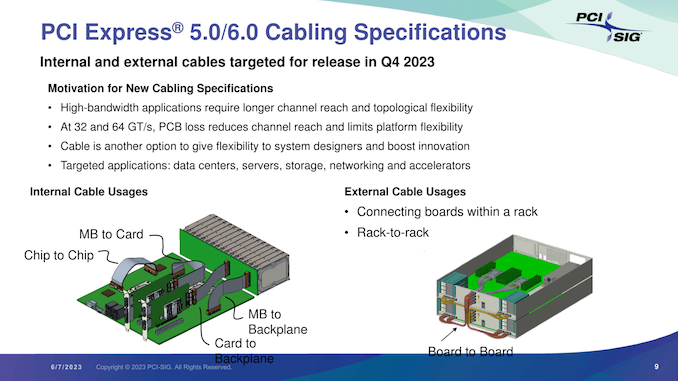

While PCIe 7.0 is in the works, the first hardware for PCIe 6.0 is still in development, and even PCIe 5.0 gear has only been around for generally less than a year. So along with their core specification development, the PCI-SIG is also working on some ancillary areas of the completed specifications, in particularly cabling.

While we traditionally think of PCIe first and foremost as a bus routed over printed circuit boards, the standard has always allowed cabling as well. And with their newer standards, the PCI-SIG is actually expecting the use of cabling in servers and other high-end devices to grow, owing to the channel reach limitations of PCBs, and how it’s getting worse with higher signaling frequencies. So, cabling is being given a fresh look as an option to maintain/extend channel reach with the latest standards, as new techniques and new materials are creating new options for better cables.

To that end, the PCI-SIG is developing two cabling specifications, which are expected to be ready for release in Q4 of this year. The specs will cover both PCIe 5.0 and PCIe 6.0 (since the signaling frequency is unchanged), with specifications for both internal and external cables. Internal cabling would be to hook up devices to other parts within a system – both devices and motherboards/backplanes – while external cabling would be used for system-to-system connections.

In terms of signaling technologies and absolute signaling rates, PCI Express trails Ethernet by a generation or so. And that means that much of the initial development on high speed copper signaling has already been tackled by the Ethernet workgroups. So, while work still has to be done to adapt these techniques for PCIe, the basic techniques have already been proven, which helps to simplify the development of the PCIe standard and cabling by a bit.

All told, cable development is decidedly a more server use case of the technology than what we see in the consumer space. But a cabling standard is still going to be an important development for those use cases, especially as companies continue to stitch together ever more powerful systems and clusters.

5 Comments

View All Comments

Xajel - Wednesday, June 14, 2023 - link

So, I should delay my upgrade to 2026./jk

pogsnet - Friday, June 23, 2023 - link

but then video cards compatible will be available at 2027back2future - Friday, June 16, 2023 - link

was searching for a table seen yrs ago, hard to find with text only search on meta search engines, but found: https://www.nextplatform.com/wp-content/uploads/20...Santoval - Monday, June 19, 2023 - link

So they retained PAM4 in PCIe 7.0 and had to double the clock to a freaking 30 GHz! The signaling noise will skyrocket with PCIe 6.0 due to PAM4, requiring error correction.The signal will get even weaker with PCIe 7.0 and *far* noisier when they need to move to PAM8(?) for PCIe 8.0 The engineering challenges involved must be immense...

Musclegaragefitness - Tuesday, September 5, 2023 - link

The progress of the PCI Express 7.0 specification is undoubtedly exciting news for the tech industry. Achieving a 512GBps connectivity milestone by 2025 showcases the relentless pursuit of faster and more efficient data transfer rates. This development will not only benefit the gaming and consumer sectors but also have profound implications for data centers, high-performance computing, and emerging technologies like AI and 5G. It's a testament to the ever-evolving nature of technology, and I'm eager to see how this advancement will shape the future of computing and connectivity.